SONET/SDH jitter measurements of high-speed OC-48 optical transceivers

By NICOLAS SCHMITT and DAVE GRANT, Agilent Technologies--SONET/SDH networks rely on highly accurate and stable synchronization to process data in and out of network elements. Any phase variations or jitter induced in the network will cause a degradation of transmission quality, bit errors, and data loss.

Thus, it's critical to understand jitter and its effect on network performance. Although jitter definitions and specifications are defined according to industry standards, test methodologies are usually left to the end user. Historically, that has manifested itself in a difficulty to achieve accurate and reproducible jitter measurements. Let's examine the measurement methods for each type of jitter, test methodology, and performance results for singlemode OC-48 (2.5-Gbit/sec) transceivers used in SONET/SDH networks.

How jitter is measured

Jitter is usually measured in unit intervals (UIs), where one UI corresponds to the phase deviation of one clock period. The percentage of jitter is calculated using the following equation:

% jitter = (Tj / T0) x 100%,

where Tj is the jitter time amplitude and T0 is the clock period. One UI represents 100% jitter. It is important to note that UIs are independent of the bit rate. And it is possible to compare jitter amplitude at different hierarchical levels in a network element.

Jitter generation is the amount of jitter present at the OC-N/STS-N output of a SONET/SDH network element in the absence of applied jitter. Two jitter parameters are defined:

• Jitter peak-to-peak — the maximum measured jitter amplitude.

• Jitter RMS — the root mean square value of the jitter signal, which provides an indication of the jitter power.

These specifications apply to the whole system of network elements. Compliance of individual components alone does not guarantee that the system will meet the SONET/SDH requirements for jitter generation. The interface between components and board layout must be carefully considered to minimize jitter generation.

At OC-48, the Telcordia GR-253 jitter generation

specification for network equipment requires <100-m UIp-p and <10-m UIrms when measured using a 12-kHz high-pass and 20-MHz low-pass filter.

Measurements are also required to determine jitter tolerance and jitter transfer. Jitter tolerance is defined as the peak-to-peak amplitude of sinusoidal jitter applied on the OC-N/STS-N input of a network element that causes an equivalent 1-dB sensitivity penalty. The jitter tolerance performance represents the ability of the clock and data recovery (CDR) circuit to recover an incoming bit sequence correctly despite the applied jitter.

Jitter transfer is defined as the ratio of jitter on the output OC-N/STS-N signal to the jitter applied on the input OC-N/STS-N signal versus frequency. The jitter transfer function is calculated using the following equation:

Jitter transfer = 20log (output jitter/input jitter),

where output and input jitter are expressed in UIs and jitter transfer in decibels (dB). Jitter transfer is comparable to a gain function where -dB and +dB indicate that the network element attenuates and amplifies jitter, respectively.

A network element's ability to pass both jitter tolerance and jitter transfer performance testing is directly linked to the bandwidth of the phase locked loop (PLL) used in the CDR circuit. Good jitter tolerance performance requires a clock recovery with high bandwidth so the PLL can track the jittered input signal and still successfully recover the clock. On the other hand, jitter transfer compliance is achieved by limiting the bandwidth of the PLL to ensure that higher frequencies are not transmitted. Thus, the successful design of a CDR circuit is always a compromise between tolerance performance and transfer compliance.

Available test methods

The three most frequently used test configurations to measure jitter require either an oscilloscope, a phase detector, or a dedicated SONET/SDH jitter analyzer. Each technique has its advantages and limitations. But to measure jitter, two main elements are required: a source that generates known amounts of jitter and a detector that accurately measures jitter. The limitations of each element must be understood to ensure the correct interpretation of the results.

A typical jitter test configuration using an oscilloscope is shown in Figure 1. This technique hinges on the ability to supply a jitter-free trigger signal. Any jitter on the trigger signal will affect the validity of the results. This method also has limitations. It is confined to one UIp-p. Above this level, the eye-diagram is totally closed. The oscilloscope is also restricted to large measurement bandwidth, which means that the noise level is usually high and no spectral information can be extracted.

Another jitter test method is when the phase detector compares the phase of the recovered clock from the network element with a jitter-free clock source. Its output is proportional to the jitter on the recovered clock. Jitter can then be measured through the appropriate bandpass filter. Figure 1 also shows a test configuration based on a phase detector, which addresses the limitations associated with the oscilloscope technique. However, it has its own limitations: It only functions at a specific data rate and requires external filters.

The ideal technique for measuring SONET/SDH jitter is with a performance analyzer. A field portable multirate SONET/SDH tester for rates up to 2.5 Gbits/sec measures the jitter performance of a network element via an optical interface. The transmitter uses a wideband PLL to generate a known amount of jitter and the receiver is based on a very-narrowband PLL to accurately extract the jitter content of the incoming signal. The multirate SONET/SDH tester uses a variety of analog and digital circuitry, combined with processing techniques to accurately generate jitter over the extensive range of amplitudes (UIp-p) and frequencies required. This jittered clock signal is used to provide SONET/SDH signals with known amounts of jitter to stress the network element or device under test.

The complete jitter measurement process requires the transparent recovery of the clock (including jitter) from the SONET/SDH signal followed by the removal of jitter from the recovered clock in the narrowband PLL to create the reference for the jitter measurements. To ensure optimum performance and accuracy, the instrument is designed and calibrated to minimize intrinsic noise in these measurement processes. That involves extensive tests during production under a variety of signal conditions to characterize and compensate for these effects.

OC-48 jitter measurements

Two different OC-48 optical transceivers installed in different reference design boards are used to demonstrate jitter measurements on OC-48 modules. The first optical transceiver is a 1300-nm laser-based duplex SC 2X9 module with integral CDR circuits. The second optical transceiver is a 1300-nm laser-based LC 2X10 small-form-factor (SFF) module. The respective reference design boards include commercially available multiplexer, demultiplexer, and CDR circuits and therefore are representative of performance that would be observed at the system level.

To accurately measure jitter, it is necessary to set the correct configuration on the jitter analyzer. Both the receiver and transmitter are set to operate at 2.5 Gbits/sec using an STS-48c (concatenated frames) pattern with a 223-1 pseudo-random bit-sequence payload. This payload has the highest low-frequency content and will therefore generate the highest amount of data-pattern-dependent jitter. The multirate SONET/SDH tester uses a built-in optical power meter; the transceiver's overload limit of -8 dBm must be respected to prevent any damage to the receiver.

A scale from -40 to 0 dBm is used in the "result" window on the jitter analyzer to display the received power. Three ranges can be identified:

• Out of range. Measurements cannot be made when the received optical power is within this range.

• BER only. Only BER can be measured accurately.

• BER and jitter. Jitter can be measured accurately when the received optical power is within this region.

The received optical power must always remain within the "BER and jitter" region when measuring jitter, since optical sensitivity will affect the results.

Jitter generation

Jitter generation measurements are illustrated using the 1300-nm 2X9 OC-48 transceiver in Figure 2. The SONET/SDH multiplexer/demultiplexer ICs, which offer an STS-48 interface, are fully integrated. In this test arrangement, differential clock and data are fed electrically into the demultiplexer. The 8-bit parallel data is then multiplexed and the serial differential outputs are AC-coupled into the optical transceiver's transmitter. The optical output is connected to the receiver of the analyzer via an optical attenuator, and the received optical power is set to -14 dBm. It is necessary to load a valid STS-48c pattern into the pattern generator to allow the analyzer to receive a valid OC-48 framed signal and ensure the measurements are made using real traffic.

To comply with Telcordia GR-253, jitter generation is measured through a bandpass filter. For the display of Figure 2, a 12-kHz high-pass and 20-MHz low-pass filter are used. All jitter generation measurements must be performed over at least a 1-minute period. Jitter generation performance for the reference design is:

• 71-m UIp-p

• 7-m UIrms

It is important to remember that jitter has many potential sources, and this result takes into account the contribution of the board, including the demultiplexer, multiplexer, transceiver, and board layout.

Jitter tolerance

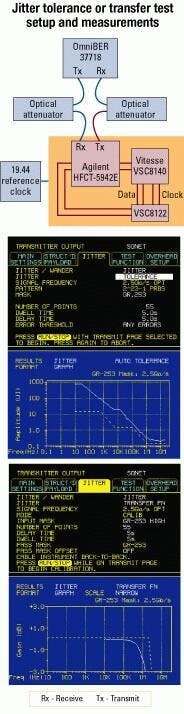

Jitter tolerance measurement is illustrated using the 1300-nm 2X10 OC-48 SFF transceiver and reference design board. The evaluation reference design board features a fully integrated SONET/SDH multiplexer/demultiplexer IC with an STS-48 interface and a multirate CDR IC capable of STS-3/-12/-48 or Gigabit Ethernet.

Figure 3 shows the test arrangement used to measure jitter tolerance. An optical OC-48 signal is generated by the transmitter of the multirate SONET/SDH tester and connected to the OC-48 SFF transceiver module's receiver via an optical attenuator. The received signal is recovered by the CDR IC and demultiplexed and multiplexed by the multiplexer/demultiplexer IC. The STS-48 electrical outputs drive the transceiver module's transmitter. The input optical power at the OC-48 transceiver is set at sensitivity plus 1 dBm.

The first result window in Figure 3 shows that the jitter amplitude (solid line) is above the tolerance mask (dotted line). The measurement also demonstrates that the CDR IC is able to track large amounts of jitter before degrading the bit-error rate. Jitter tolerance is an important parameter since it indicates how CDR circuits perform in the presence of jittered signals.

Jitter transfer

Before measuring jitter transfer, it is necessary to perform an internal calibration of the instrument. The multirate SONET/SDH tester is looped back optically on itself via an optical attenuator, and the input optical power is set to -14 dBm. During calibration, jitter measured by the receiver is correlated to jitter generated by the transmitter.

The second result window in Figure 3 shows that the jitter gain (solid line) is below the transfer mask (dotted line). As this measurement shows, the CDR does not amplify or pass through jitter over the defined frequency range, but instead it rolls off below 1 MHz (the mask rolls off at 2 MHz). Jitter transfer compliance is essential to prevent jitter accumulation in a network, especially if it includes the use of a repeater.

Nicolas Schmitt and Dave Grant are customer support engineers at Agilent Technologies' Networking Solutions division locations in Ipswich and South Queensferry, UK, respectively. They can be reached at [email protected] and [email protected].

Figure 3. Setup for either jitter tolerance or jitter transfer measurement. The first screen displays jitter tolerance, indicating that the jitter amplitude (solid line) is above the tolerance mask (dotted line). The second screen displays jitter transfer and shows that the clock and data recovery does not amplify or pass though jitter over the defined frequency range, but rather rolls off below 1 MHz.