John Bergen, I-Cube Corp.

Developing an understanding of basic switch architectures is the first step in understanding switch selection. Designers have traditionally based their networks on three basic interconnect architectures: shared bus (also known as multidrop); ring interconnect using point-to-point architecture; and the crossbar switch. Shared-bus architectures can be constructed from widely available standard products. Despite these advantages, shared-bus architectures suffer from the bandwidth limitation of one data transfer at a time and the inability to cost-effectively scale with higher clock rates and data paths. As a result of these physical constraints and the need for cost-effective solutions, design engineers find that shared-bus architectures have practical performance limits.

Ring architectures overcome the limited data-transfer rates of shared buses by using concurrent data transfers to achieve higher aggregate bandwidths. However, ring architectures suffer from high latency during data transfers, the lack of cost-effective components, and reliability issues such as single points of failure.

Given the limitations of these first two architectures, many designers are now using crossbar switches that are based on an idea implemented in electromechanical assemblies first used in early telephone switching offices.

A crossbar switch network is constructed from crosspoint switches that form a crosspoint-switching matrix. Closing the "switch" at the appropriate crosspoint in the matrix creates a connection between an input and output.

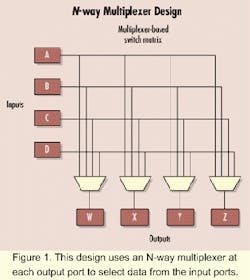

Crosspoint switches offer several benefits for the designer. High-performance crossbar switches are nonblocking, erasing the bandwidth limitations of one-at-a-time connections. They also have the flexibility to connect any input to any output.The other design methodology uses a crosspoint array (see Figure 2) that has a switching element at each input/output (I/O) intersection. This method provides a high-density crosspoint array, offering greater flexibility than traditional crossbar switches, making it feasible to build large switches in a cost-effective way using modern complementary metal-oxide semiconductor (CMOS) technology.

Designers can implement switches in a variety of device types, including field-programmable gate arrays (FPGAs), application-specific integrated circuits (ASICs), and application-specific standard products (ASSPs).

FPGAs offer the flexibility of reprogrammability and may contain additional functionality, complementing the blocks dedicated to the switch fabric. Many designers are familiar with this product architecture, and FPGA manufacturers are regularly introducing new products with additional features at lower costs. However, FPGAs also have significant limitations. Most FPGA architectures do not have the ability to handle the large number of high-data-rate signals needed to create flexible high-performance switching fabrics.

ASIC designs offer the potential to be complete systems-on-a-chip (SOCs). ASICs are a cost-effective solution for high-volume designs that are price-sensitive or have limited switching functionality. As is also the case with FPGAs, an ASIC arch itecture may not be easily scalable for high-port-count switching. Also, ASICs are difficult and costly to modify once they are completed and re strict the designer's ability to reuse them in future projects.

ASSPs are a broad category of ICs that are used to define those standard products that do not fit neatly into a larger, more easily defined product category. The crossbar switch is a relatively new category of ASSP. These devices offer designers faster time-to-market than ASICs because they are "off-the-shelf" solutions, and they provide better switching performance than FPGAs. However, because these products are dedicated solely to switching, they do not offer the ability to integrate additional functionality, such as can be provided by FPGAs and ASICs.

There are two basic types of high-performance ASSP cross bar switch devices available from IC manufacturers. The multiplexer-based crosspoint products from certain suppliers are built on costly bipolar or gallium arsenide processes that result in very-high-performance switching. The nonreturn-to-zero data rate of these crosspoint switches typically ranges up to 2.5 Gbits/sec in flow-through mode.

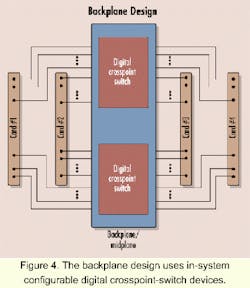

The low-voltage swing of these devices makes them less susceptible to noise, reducing the crosstalk and ground-bounce effect. These types of switches are suitable for high-speed switching applications, including optical communications and high-definition video systems with data rates of 270 Mbits/sec and above.Another category of CMOS reprogrammable digital crosspoint switches (DCSs) is targeted for I/O-intensive communication system designs. Unlike the crosspoint switches already mentioned, which are usually limited to a maximum of 64 inputs by 64 outputs, these crosspoint-switch devices are available in switch matrices of up to 532 I/Os, each of which can be configured as either an input or output. These products are ideal for applications that not only require a large number of I/Os, but also require a high degree of flexibility. Any-input-to-any-output connections, the ability to handle multiple outputs (for multicast or broadcast applications), and configurable I/Os are important features. They enable these devices to be used in systems that must handle multiple input and output speeds for a range of protocols such as digital crossconnects and multiservice gateway devices. Ad ditionally, these devices de monstrate the crosspoint's capability to make systems scalable and modular.

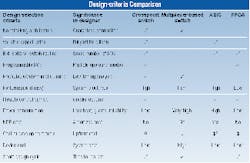

The Table shows a comparison of the different switch implementations available.

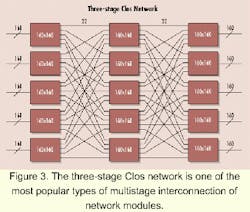

The idea of constructing large switch networks from smaller switch elements is a fundamental technique for most switch architectures. However, a basic limita tion becomes apparent when there is a need to build larger crosspoint switch networks. When the switch fabric is doubled, it requires four times as many chips. For example, scal ing a 64x64 output switch up to a 128x128 output switch requires four 64x64 switches. This methodology can be unwieldy and costly as more and more devices are needed to build a larger switch network.

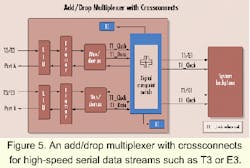

Crosspoint switches are often used in multistage schemes that can be used to create nonblocking switch networks. There are several ways to interconnect switch modules. The most popular one is the multi stage interconnection of network modules. Figure 3 illustrates the three-stage Clos network, which is a well-known example of such an interconnection.Another application for crosspoint switching is illustrated in Figure 5. This diagram shows an add/drop/bypass multiplexer with crossconnects for high-speed serial data streams such as T3 (44.736 MHz) or E3 (34.46 MHz). In this system, digital streams of the same bit rates are received on two ports. The signals are converted into single-ended transistor-transistor logic levels using clock recovery and frame synchronization circuits, shown as a line interface unit and framer in Figure 5. This data stream is then applied to a T3 or E3 multiplexer/demultiplexer device, which breaks the data stream into its subrate tributaries. As the T1 (1.544 MHz) and E1 (2.048 MHz) constitute the basic time-division multiplexing (TDM) data/voice circuits for T3 and E3, respectively, the multiplexer/demultiplexer device has either 28 or 16 data and clock output and input lines.

While digital crossconnects, add/drop multiplexers, and backplanes are traditional applications for crosspoint switches, there are many new applications in emerging markets. For example, a recently introduced media gateway uses crosspoint devices to form the switch fabric. This system can switch TDM and voice-over-Internet-protocol (VoIP) traffic across packet networks. The crosspoint switch adds to the system's flexibility by enabling the offload of TDM and VoIP traffic across a range of interfaces and backbone networks.

Today's designers have a number of options available to them to solve their switching problems. Their decision must be based on the specific design requirements for their application. This selection process will include the consideration of a variety of product types, features, and performance. q

John Bergen is the product marketing manager for I-Cube Corp. (Campbell, CA), which specializes in high-performance crosspoint-switching integrated circuits.

This article appeared in the May 2000 issue of Integrated Com munications Design, Lightwave's sister publication.

Switching-fabric integrated circuits are at the heart of a wide variety of telecommunications systems such as add/drop multiplexers, digital crossconnects, and media gateways. De signers can choose from a variety of switch implementations, ranging from application-specific standard products (ASSPs), application-specific integrated circuits (ASICs), or field-programmable gate arrays (FPGAs). The selection of any one of these solutions will be based on a variety of factors, including cost, performance, scalability, and systems criteria. There are several basic switch selection criteria:

Nonblocking. Most switch fabrics used in telecommunications equipment are nonblocking, which is the ability to guarantee delivery of data through the switch from any input to any output. Any attempt to create a valid connection through a nonblocking switch will succeed.

Scalability. Most telecommunications networks and computer systems are designed to be scalable. By adding one or more "modules" to the existing system, these systems can be expanded. The ability to create larger switch networks from smaller switch elements is a basic fundamental of most switching architectures.

Performance metrics. Switch ICs cover a wide range of performance metrics, such as clock rate and data throughput, depending on the design and technology. Data-throughput rate and operating frequency are key criteria. Given the wide range of options, designers will match the switch selection with the appropriate application. For example, new optical-networking components, operating at data rates surpassing 622 Mbits/sec (OC-12) will require higher-speed devices than digital crossconnects that may be handling T1 (1.54 Mbits/sec) or E1 lines (2.048 Mbits/sec).

Signal integrity. Consistent timing over any path in the switch is an important characteristic, so that the switch fabric has high fanout and tight clock skew to simplify the design and increase switch reliability.

Flexibility. The ability to easily configure switch ports as inputs, outputs, or bidirectional signals gives designers the flexibility to easily create a variety of switch matrices. The flexibility to control each I/O with a choice of clocking, input-enable, and output-enable options also adds to the flexibility of the switch.

Reconfigurability. Switch matrices that can be reconfigured on the fly offer designers the flexibility of changing their switch configuration without replacing the switch IC.

-John Bergen